如何对你的第一个 FPGA 器件进行编程

本教程将向您展示如何创建“Hello World”的硬件等效版本:一个闪烁的LED。

获取新的Intel® IoT Developer Kit,这是一个完整的硬件和软件解决方案,使开发人员能够使用Intel® Galileo和Intel® Edison开发板创建令人兴奋的新解决方案。访问Intel® IoT开发者中心。

本教程将向您展示如何创建“Hello World”的硬件等效版本:一个闪烁的LED。这是一个简单的练习,帮助您开始使用Intel® Quartus®软件进行FPGA开发。您将学习如何编译Verilog代码、进行引脚分配,然后对FPGA进行编程以闪烁开发板上的八个绿色用户LED之一。您将使用一个50 MHz的时钟输入(开发板上有一个振荡器驱动FPGA中的计数器)来创建一个计数器,并将一个板载LED分配给计数器的第n位。

级别:初学者

材质

硬件

Terasic DE10-Nano 套件

Terasic DE10-Nano开发板基于Intel® SoC FPGA,为创客、IoT开发者和教育工作者提供了一个可重构的硬件设计平台。您可以在这里购买套件。

软件

Intel® Quartus® Prime软件套件精简版

这里使用的FPGA设计软件非常适合初学者,因为它免费下载且无需许可证文件。您可以在这里下载该软件。

注意:安装文件非常大(几个GB)。如果您的磁盘空间不足,我们建议您只下载本次练习所需的文件。在提示选择要下载的文件时。选择“individual files”选项卡,然后勾选Quartus Prime和Cyclone V device support。

如果您已下载并安装了Intel® Quartus®软件,让我们开始创建一个项目吧!

注意:屏幕截图基于最新版本v16.1。使用早期或晚期版本的Intel® Quartus®软件时,用户体验可能会有所不同。

步骤1:创建Intel® Quartus®软件项目

步骤1.a:打开Intel® Quartus® Prime软件套件精简版。

步骤1.b:打开新建项目向导

步骤1.c:选择下一步

步骤1.d:目录、名称、顶层实体

选择一个目录来存放您的项目。在这里,我们将项目命名为“Blink”,并将其放在intelFPGA_lite文件夹下,但您可以将其放在任何您想放的地方。选择下一步。

当提示创建目录时,选择是。

步骤1.e:项目类型

选择空项目,然后单击下一步。

步骤1.f:添加文件

这里不添加任何文件。单击下一步。

步骤1.g:系列、设备和开发板设置

选择以下选项:

系列:Cyclone V

设备:Cyclone V SE Base

设备名称:5CSEBA6U23I7

点击**下一步**。

步骤1.h:EDA工具设置

跳过此部分。单击下一步。

步骤1.i:摘要

点击**完成**。

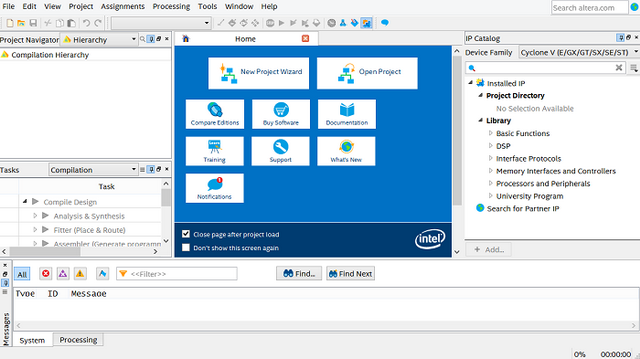

将显示以下屏幕。

步骤2:创建HDL文件

硬件描述语言(HDL)

我们使用Verilog作为HDL。如果您熟悉C编程语言但对HDL编程不熟悉,Verilog与C类似,您需要在每个语句的末尾加上分号“;”。

步骤2.a:导航到“文件”选项卡(主窗口),然后选择新建。

选择Verilog HDL File,然后单击OK。

步骤2.b:选择文件 > 另存为。将文件名设置为“blink”。这是您的顶层文件名,必须与项目名称(blink)匹配。单击保存。

步骤3:创建Verilog模块

步骤3.a:将此Verilog代码复制并粘贴到blink.v窗口中,然后保存文件。

// create module

module blink(clk, LED);

input clk; // input clock 50MHz

output LED;

// create a binary counter

reg [31:0] cnt; //32 bit counter

initial cnt <= 0; // start count at zero

always @(posedge clk) cnt <= cnt+1; // count up

//assign LED to nth bit of the counter

assign LED = cnt[24]; // Use the 25th bit of the counter to blink the LED at a few Hz

endmodule

步骤3.b:分析与合成

运行“分析与合成”(右键单击,然后单击开始)以对Verilog代码执行语法检查。

如果过程成功完成,则“分析与合成”旁边会显示绿色复选标记。如果出现错误,请检查您的语法,并确保其与上面提供的代码块完全匹配。请记住,Verilog与C类似,使用分号来结束语句。确保分号放置正确。

步骤4:选择引脚分配

步骤4.a:在顶部导航栏中,选择分配 > 引脚规划器。

请注意,输入(clk)和输出(LED)已列在“节点名称”下。这是因为您已经运行了“分析与合成”。

步骤4.b:Terasic DE10-Nano用户手册的表3-8(第26页)显示了LED的引脚分配。选择8个绿色用户LED中的一个。表3-5显示了时钟输入的引脚分配。在本教程中,您将使用FPGA的50 MHz时钟输入。

在位置列中输入引脚编号。其余列将自动填充数据(有些带有我们需要设置的默认值)。您需要更改的列是I/O标准、驱动强度和压摆率。对于I/O标准,默认值为2.5伏。更改为3.3-V LVTTL。驱动强度默认值为16ma(default),我们需要选择16ma。如果我们不专门设置它们,编译时会收到警告消息。此外,将压摆率从1(default)更改为1。您不需要为时钟设置压摆率。将其留空。

| 节点名称 | Location | I/O 标准 | 驱动强度 | 压摆率 |

|---|---|---|---|---|

| LED | PIN_W15 | 3.3-V LVTTL | 16ma | 1 |

| clk | PIN_V11 | 3.3-V LVTTL | 16ma |

设置引脚位置。

将输入(clk)和输出(LED)的驱动强度设置为16ma。将压摆率设置为1(仅适用于LED)。

关闭引脚规划器。

步骤5:创建SDC文件

在编译Verilog代码之前,您需要为设计提供时序约束。您将创建一个SDC(Synopsis Design Constraints)文件,其中包含命令,让Intel® Quartus®软件知道如何完成设计的时序。没有它,您将在编译流程中收到警告消息,因为Intel® Quartus®软件不知道如何完成设计的时序。

要创建blink.sdc并将其添加到blink文件目录中,请执行以下操作。

打开一个文本编辑器(记事本)并复制粘贴以下内容

# this is a comment # inform quartus that the clk port brings a 50MHz clock into our design so # that timing closure on our design can be analyzed create_clock -name clk -period "50MHz" [get_ports clk] # inform quartus that the LED output port has no critical timing requirements # its a single output port driving an LED, there are no timing relationships # that are critical for this set_false_path -from * -to [get_ports LED]

现在将其另存为.sdc文件。将其放在blink文件目录中 – 与我们的Verilog文件(.v文件扩展名)所在的目录相同。

步骤6:编译Verilog代码

步骤6.a

右键单击编译,然后单击开始。由于只有几行代码,编译应该需要大约一分钟。

注意:要编译代码,您暂时不需要将Terasic DE10-Nano开发板连接到计算机。很快就要用了!(提示:拿出盒子里附带的迷你USB线)。

编译Verilog代码后,您就可以对FPGA进行编程了。

步骤7:编程FPGA

最后一步是对FPGA进行编程。为此,您需要通过USB Blaster端口将开发板连接到计算机。

注意:在对FPGA进行编程之前,请移除microSD卡。

步骤7.a:使用Terasic DE10-Nano套件附带的USB线(mini-b连接器)。将mini-b连接器插入Terasic DE10-Nano开发板上的USB Blaster端口,将Type-A端插入主机计算机的标准USB端口。

步骤7.b:打开开发板电源。

步骤7.c:右键单击以打开编程设备。

步骤7.d:硬件设置

选择硬件设置。

将模式设置为JTAG。

在“当前选定的硬件”下拉菜单下,选择DE-SoC。

单击关闭。

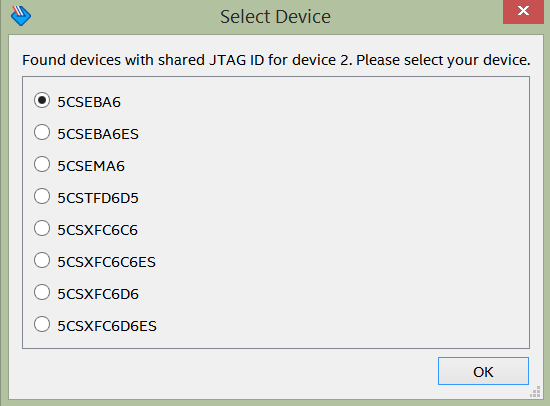

步骤7.e:单击自动检测。

选择设备5CSEBA6。这是FPGA设备。

步骤7.f:添加.sof文件。

右键单击FPGA设备的“文件”列,然后单击更改文件。

步骤7.g:导航到output_files文件夹,选择blink.sof,然后单击打开。

在这里,blink.sof是您的编程文件。SRAM对象文件(.sof文件)是包含配置SRAM基设备(我们的FPGA基于SRAM)数据的二进制文件,使用Intel® Quartus®软件的“编程设备”(也称为Programmer)。Programmer读取SOF文件并获取设备的编程比特流。

在“编程/配置”列中打勾,然后单击开始。

步骤8:观察闪烁的LED

如果您的进度条显示100%(成功),请观察开发板上的LED闪烁。

后续步骤

现在您已经成功地让一个LED闪烁了,您可以通过使用计数器的不同位来修改LED的闪烁速率。1赫兹是1/秒(每秒周期数),以1 Hz闪烁意味着LED每秒闪烁一次。对于2 Hz,LED每秒闪烁两次。而0.25 Hz将使LED每4秒闪烁一次(慢闪)。要实现更慢的闪烁,请使用计数器的高位,要实现更快的闪烁,请使用低位(例如,cnt[22])。尝试不同的计数器位,看看会得到什么结果。

下面是一些快速的时钟和计数器数学计算,可以帮助您理解闪烁频率与所选时钟和计数器位之间的关系。

时钟和计数器数学

cnt[n],其中n = 计数器位

2^n;我们在Verilog代码示例中选择了n = 24

2^24 = 16,777,216

我们的时钟是50 MHZ或50,000,000

时钟 / 2^n = 每秒闪烁次数<br /> 50,000,000 / 16,777,216 = 2.9802

这大约是每秒3次闪烁。