启用 FPGA 以供软件开发人员使用

0/5 (0投票)

提升汽车、网络和云计算的效率和性能

现在是审视现场可编程门阵列 (FPGA) (图 1) 的绝佳时机。得益于 FPGA 新的编程能力,一个计算新时代正在崛起。随着全球数据量的激增,人们对具有定制芯片设计的、功耗高效的计算能力有着巨大的需求——同时又需要 FPGA 的灵活性。

在本文中,我们将分享我们的观点,探讨如何真正地为所有领域的软件开发者启用 FPGA——包括我们将重点讨论的三个领域:

- 汽车

- 网络(例如,5G)

- 端到端云计算(例如,数据中心)

通过讨论加速栈和开放可编程加速引擎 (OPAE),我们对如何赋能数据中心进行了更深入的探讨。我们不会深入探讨任何特定领域,例如机器学习,尽管完整的解决方案栈可以通过封装 FPGA IP(例如,为利用 FPGA 而实现的库例程)来支持它。但是,我们将提供一些链接,以帮助您更深入地了解英特尔正在引领的、易于访问的 FPGA 编程新世界。

什么是 FPGA?

FPGA 本质上是一个空白的画布,等待我们为其绘制电路设计。我们通过编写所需数字电路的描述,然后将其编译(FPGA 开发者称之为综合)成一个配置文件(称为位文件),最后将其加载到 FPGA 中来完成此操作。一旦加载完成,FPGA 的行为就如同我们设计的数字电路。

FPGA 从未被永久编程。当断电时,它们不会保留其程序(位文件/比特流)。在大多数系统中,FPGA 在上电时会被加载——要么从 FPGA 板上的固件加载,要么由主机处理器以编程方式加载。我们可以随时重载 FPGA 以更改其功能。

FPGA 高度并行化的架构意味着在 FPGA 上运行计算将比软件提供更好的性能、更低的功耗、更低的延迟和更高的吞吐量。想象一下,能够配置一个函数的硬件实现,并在我们的程序中使用它。正如我们将要讨论的,FPGA 领域最热门的话题是如何使 FPGA 编程对软件开发者更加易于访问。英特尔正在引领实现这一目标。

数据爆炸

在三个关键领域,英特尔® FPGA 在提供更快的速度、超低延迟、功耗效率和巨大的灵活性方面发挥着重要作用:自动驾驶和辅助驾驶、加速网络(包括 5G 和软件定义网络,或 SDN)以及云计算(包括高性能深度神经网络,或 DNN 推理)。在这三个应用场景中,大数据是 FPGA 并行处理架构如此关键的原因之一。

自动驾驶汽车

自动驾驶汽车(包括提供自动驾驶功能的车辆)的实现依赖于车载计算、网络和数据中心的协同工作。自动驾驶汽车会生成并使用海量数据来安全导航。它需要大约 1GB/秒的实时处理能力,并且出于安全原因,从感知到反应的时间必须小于一秒。例如,英特尔的处理能力是 2018 年 Audi A8* 自动驾驶系统 的一部分。在该设计中,英特尔 FPGA 负责处理自动驾驶汽车的物体融合、地图融合、停车、预碰撞、处理和功能安全等方面。

网络和 5G

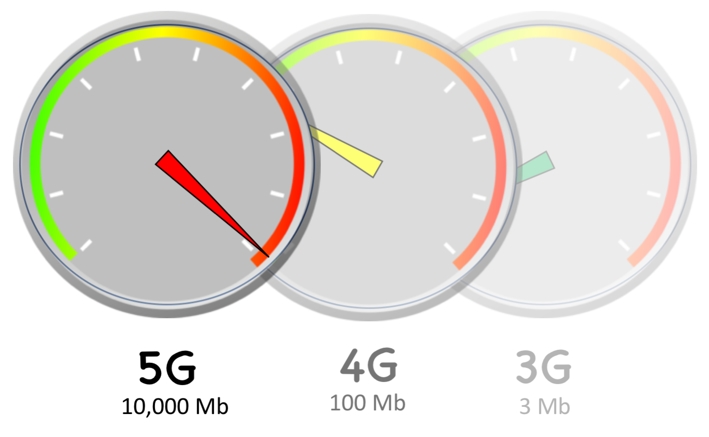

网络正在迅速扩展,带宽增加 1000 倍,设备增加 100 倍,并且要求端到端往返时间达到 1 毫秒。FPGA 在满足这些需求方面至关重要。目前支持 100Gb/秒的设备刚刚开始普及,而 IEEE 802.3 的 400 Gb/秒以太网研究组(始于 2013 年)预计今年将出台 400Gb/秒的标准。随着 5G 标准化工作的全面展开,我们正接近一个临界点,即无线网络承载的数据量将超过纯有线网络(图 2)。

云计算

IDC 表示,全球总数据量从 2013 年的约 4.4 ZB,2015 年的 8.6 ZB,增长到 2020 年的 44 ZB,届时预计将有高达 500 亿台设备连接到互联网。云计算在数据中心、边缘以及它们之间的所有地方都有需求。它需要规模、吞吐量、每瓦性能、灵活性和低延迟。同样,FPGA 在满足这些需求方面至关重要。

计算的必然要求:更多并行性、更低功耗、更大灵活性

为了理解这海量数据,我们需要实现决策自动化,对连接设备提供实时洞察,并为用户提供与数据交互的直观连接。没有加速计算,许多应用程序(例如,人工智能)的横向扩展将是不切实际的。新的计算需求要求前所未有的并行性、更低的功耗以及在加速器中前所未有的灵活性。为了满足这一需求,从边缘到云端的硬件平台一直在演进,包含 CPU 和加速器的混合体。FPGA 在朝着高度并行、功耗高效且可重构的异构计算平台发展方面发挥着关键作用。简而言之,FPGA 实现了硬件性能和软件的可编程性。然而,FPGA 编程模型通常以硬件为中心。随着 FPGA 成为计算环境的标准组件,用户期望硬件是软件定义的,因此 FPGA 不仅应该由硬件开发者访问,还应该由软件开发者访问。

面向软件世界的 FPGA 编程

FPGA 已经存在多年,用于解决硬件设计问题。其编程方式完全采用硬件设计者熟悉的术语,而不是通过任何专为软件开发设计的编程语言。旨在支持软件开发而非仅仅硬件替换设计的新 FPGA 设计,以及新的软件开发工具,使得 FPGA 编程值得软件开发者认真考虑。

这种转变让我们想起 GPU 编程方法的演变,但有一个优势是 FPGA 并非为特定用途(即图形处理)预先设计。这种灵活性开启了一个前所未有的计算新时代。

完善 FPGA 的解决方案栈

作为可编程加速器的 FPGA 先驱们,在极少的工具帮助下,已经走了很长的路。他们通过使用硬件描述语言 (HDL),如 Verilog* 或 VHDL* 进行编程,始终如履薄冰地徘徊在硬件设计世界。几年前,我们调查了对 FPGA 开发感兴趣的人。一个令人玩味的评论是:“有一个 FPGA 开发者社区,[各种 FPGA] 论坛都相当活跃;并且有大量的文献可用。话虽如此,但这是一个以硬件工程师为主的社区——软件开发者可能很难得到他们问题的答案。” 尽管情况正在改变,但这个评论仍然非常重要,因为在接受调查的人中,不到十分之一的人虽然表示对 FPGA 感兴趣,但仍然舒适地使用 VHDL 或 Verilog 进行编程。在同一群体中,超过 90% 的软件开发者知道 C、C++ 或 OpenCL*,并且超过 75% 的人表示他们更愿意依赖库来利用 FPGA 的功能。因此,英特尔下一代 FPGA 工具专注于 C、C++、OpenCL 和库是合乎情理的。

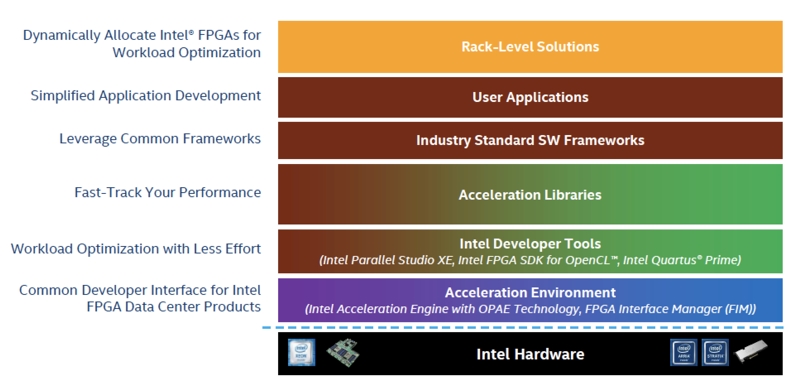

软件栈一如既往地依赖于硬件流程,但完整的解决方案栈(图 3)提供了编程层,从而实现了高效但对软件友好的接口。这些新方法并没有抛弃传统的 FPGA 工具——它们仍然可用,并且自身也有改进。然而,通过完整的 FPGA 解决方案栈,编程方式与我们在 CPU 世界中发现的类似——深入的架构专业知识融入了编译器和库中,这些库对那些专业知识属于其他领域(即计算机体系结构以外的科学和工程学科)的程序员来说是可访问的。应用程序开发者通过 FPGA IP 使用 FPGA,而 FPGA IP 的开发者之间存在关注点的分离。完整的解决方案栈使得这种思考 FPGA 编程的新方式成为可能。

适用于集成 FPGA 的 Intel® Xeon® 处理器加速栈

英特尔正在投资 FPGA 设计、编程工具和库,以实现 FPGA 的完整解决方案栈。我们将讨论这是如何在云计算中实现的,特别是在数据中心内部。

适用于集成 FPGA 的英特尔® 至强® 处理器加速栈(图 4)是英特尔设计和分发的强大软件、固件和工具集合,旨在简化英特尔 FPGA 的开发和部署,以优化数据中心的负载。它提供了优化的简化硬件接口和软件 API,以便软件开发者可以专注于其自身解决方案的独特增值。通过我们通用的英特尔 FPGA 开发者接口,前所未有的代码重用现在成为可能。为了更快地推向市场,我们为某些领域提供了系统优化的参考库,使得几乎没有 FPGA 经验的应用程序开发者也能利用英特尔 FPGA 来大幅提升性能。

在软件世界中使用 FPGA 的优雅解决方案

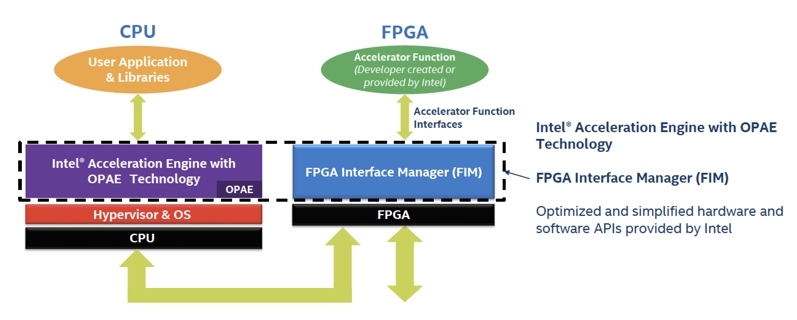

英特尔旨在通过普通的库调用来普及 FPGA。早期的 FPGA 用户成功地采用了类似的方法,但缺乏可移植的标准。考虑一个标准的框架(图 5),它为

- 应用程序开发者 提供了一个标准的框架或 SDK 来指示所需的功能,然后提供这些功能的 FPGA 加速版本。这些开发者继续使用 C、C++、Fortran 或其他具有 C 接口的高级语言(例如,Python*)进行编程。这使得用户可以利用更广泛的开源和商业工具开发者社区。

- 系统 提供了一种标准的方式来访问和使用它们部署的 FPGA。例如,数据中心运营商可以在其加速栈中使用开放可编程加速引擎 (OPAE) 来管理数据中心环境中的 FPGA。

- FPGA 代码开发者 提供了一种标准的方式来打包和共享加速例程。这些开发者将使用 OpenCL 或其他方法(例如,VHDL 或 Verilog 等 HDL/RTL)来精确调整和导出其 FPGA 例程。

系统所有者使用该框架来允许应用程序加载/卸载它们所需的 FPGA 包。应用程序开发者使用该框架来请求和使用 FPGA 包,同时仍然使用高级语言进行所有编程。FPGA 程序员可以使用低级语言来创建 FPGA 模块,并将它们打包供应用程序开发者使用。

开放可编程加速引擎 (OPAE)

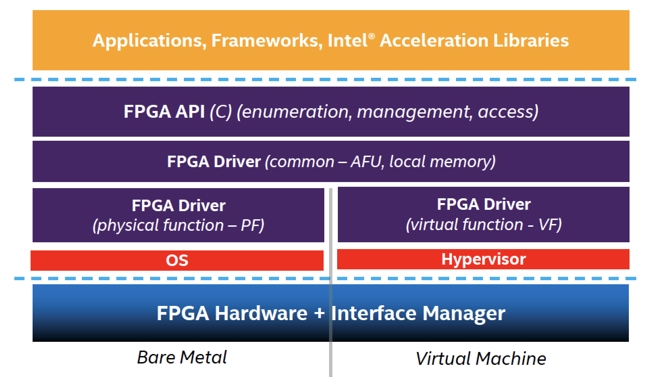

为了帮助在数据中心实现这个加速栈,英特尔创建了开放可编程加速引擎 (OPAE)(图 6)。OPAE 在处理器上运行,并处理 FPGA 重配置过程的所有细节。OPAE 还提供库、驱动程序和示例程序,可用于开发 FPGA 例程。它通过抽象硬件特定的 FPGA 资源细节,在不同产品代之间提供一致性。它设计用于最小的软件开销和延迟,并提供了一个轻量级的用户空间库 (libfpga)。OPAE 支持虚拟机和裸金属平台。

OPAE C API 允许软件系统与 FPGA 进行接口。API 提供设备或平台特定的扩展,用于模拟目标体系结构的特定功能。例如,英特尔创建了一个平台特定的 API 扩展,用于暴露集成 FPGA 的英特尔® 至强® 处理器相干内存互连上的低延迟通知机制,该机制包含在英特尔 FPGA IP 库中。

英特尔 FPGA 的一个关键能力是能够动态地重新配置 FPGA 的一部分,而其余设计则继续运行。这使得我们可以在运行时重新配置 FPGA 的区域,以根据需要实现不同的功能。OPAE 利用了通过不同比特流进行的部分可重配置。这是 FPGA 术语,指的是编译后的 FPGA 程序。FPGA 接口管理器 (FIM,昵称蓝比特流) 包含支持 FPGA 加速器的逻辑,包括 PCIe* IP 核、CCI-P* fabric、板载内存接口和管理引擎。加速器功能单元 (AFU,昵称绿比特流) 是我们自定义功能的编译版本。AFU 是在 FPGA 逻辑中实现的加速计算例程,OPAE 将其卸载到英特尔 FPGA 以提高性能。OPAE 支持同一 FPGA 上的多个 AFU 插槽。这使得我们可以将 AFU 视为应用程序可以加载和使用的 FPGA 加速函数库,并且可以同时拥有多个库(AFU)。

英特尔还支持 AFU 模拟环境 (ASE),这是英特尔® QuickAssist Accelerator Abstraction Layer 软件开发套件中提供的一个代码开发和仿真工具套件。它允许针对 AFU 模拟测试 OPAE 启用的软件应用程序。它旨在提供一致的事务级别硬件接口和软件 API,使用户能够开发和调试生产质量的 AFU 和主机应用程序,这些应用程序随后可以无需修改即可在实际 FPGA 系统上运行。

FPGA IP 库:加速库

我们之前提到,FPGA 专家有大量的机会继续使用 RTL/HDL 编写高度优化的代码。然而,FPGA 的新特性在于能够以标准化的方式将这种专业知识打包成库,供非 FPGA 专家的应用程序开发者使用。我们将这类库称为 FPGA IP 库,编写它们的可能性似乎无穷无尽。FPGA IP 库可以帮助机器学习、基因组学、数据分析、网络、自动驾驶、波束成形等各个领域的应用程序,以及任何可以通过 FPGA 进行硬件加速以实现巨大并行性、低延迟、灵活且功耗高效的功能的应用。不出所料,英特尔已主动编写了一个 FPGA IP 库,以帮助实现基本但重要的 FPGA 使用功能。这个库有助于其他人入门,并作为 FPGA IP 库及其如何轻松集成到完整解决方案栈的示例。

Intel FPGA IP 库

Intel® FPGA IP 库是一个轻量级的用户空间库,为计算环境中的 Intel FPGA IP 资源提供抽象。该库构建在支持 Intel FPGA IP 设备的驱动程序栈之上,抽象了硬件和操作系统 (OS) 特定的细节,并将底层 Intel FPGA IP 资源公开为一组在主机上运行的软件程序中可访问的功能。

这些功能包括设备上预先配置的加速逻辑,以及管理和重新配置设备的函数。该库使用户应用程序能够透明且无缝地利用基于 Intel FPGA IP 的加速。

通过提供统一的 C API,Intel FPGA IP 库支持不同类型的集成和部署模型,从具有一个或多个 Intel FPGA IP 设备的单节点系统到数据中心的大规模部署。例如,一个简单的用例是,运行在具有 Intel FPGA IP PCIe 设备的系统上的应用程序可以轻松使用 Intel FPGA IP 来加速某些算法。在另一端,数据中心的资源管理和编排服务可以使用此 API 来发现和选择 Intel FPGA IP 资源,然后将它们划分给具有加速需求的任务使用。

Intel FPGA SDK for OpenCL

对于希望在英特尔 FPGA 上创建自定义加速器功能的 FPGA 开发者,加速栈提供了 Intel® FPGA SDK for Open Computing Language (OpenCL)。OpenCL 是一种行业标准、基于 C 的编程语言,它允许用户抽象传统的硬件 FPGA 开发流程,并使用更快、更高级的软件开发流程。使用 Intel FPGA SDK for OpenCL,您可以在 C 中使用高级软件流程来开发 FPGA 设计。我们可以在几秒钟内模拟 x86 主机上的 OpenCL C 加速器代码,获得详细的优化报告,其中包含具体的算法流水线依赖信息,或者在几分钟内原型化虚拟 FPGA fabric 上的加速器内核。

摘要

英特尔在 FPGA 领域以高度可编程的 FPGA 解决方案处于领先地位。现在是审视 FPGA 编程方面的好时机。摩尔定律为 FPGA 设计者提供了大量可用的资源,而设计者反过来又利用这些晶体管添加了考虑软件可编程性的功能。OpenCL 极大地促进了 FPGA 开发者与应用程序需求的连接。现在,英特尔发布了一个框架,帮助系统所有者、应用程序开发者和 FPGA 程序员以标准化的方式进行交互——通过通用的开发者接口、工具和 IP,更容易地利用 FPGA 和重用代码,这是一个真正的优势。